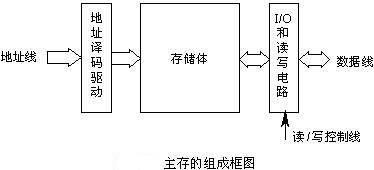

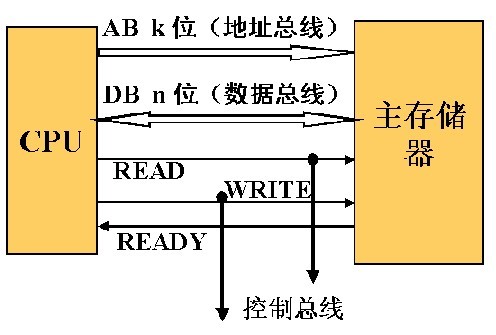

гҖҖгҖҖCPUе°�(duГ¬)еӯҳе„І(chЗ”)еҷЁйҖ�(jГ¬n)иЎҢи®ҖеҜ�(xiДӣ)ж“ҚдҪң��пјҢйҰ–е…Ҳз”ұең°еқҖзёҪз·ҡзөҰеҮәең°еқҖдҝЎиҷҹ(hГ o)����пјҢ然еҗҺзҷј(fДҒ)еҮәи®Җж“ҚдҪңжҲ�?qЕ«)жҮ–еғ®йһҜзӣ®еҲӮиҸ©зӣ�?hГ o)�пјҢеңЁж•�(shГ№)ж“�(jГ№)зёҪз·ҡдёҠйҖ�(jГ¬n)иЎҢдҝЎжҒҜдәӨжөҒгҖӮеҰӮжһңе°Үз”ұиӢҘе№Іеӯҳе„�(chЗ”)иҠҜзүҮж§�(gГІu)жҲҗзҡ„еӯҳе„І(chЗ”)еҷЁе’ҢCPUзңӢеҒҡе…©еҖ�(gГЁ)й»‘зӣ’еӯ������пјҢйҖҡйҒҺ(guГІ)ең°еқҖзёҪз·ҡпјҲABпјүгҖҒж•ё(shГ№)ж“�(jГ№)зёҪз·ҡпјҲDBпј�����гҖҒжҺ§еҲ¶зёҪз·ҡпјҲCBпјүзӣёиҒ�(liГЎn)зҡ„зөҗ(jiГ©)ж§�(gГІu)еҰӮең–жүҖзӨ������гҖ�

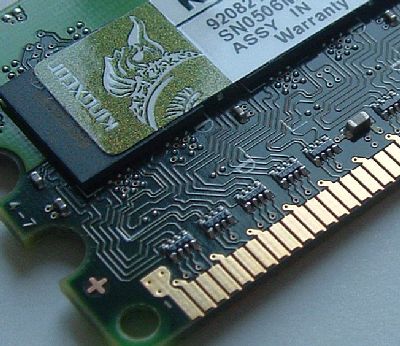

дё»еӯҳе„�(chЗ”)еҷЁиҲҮCPUзҡ„йҖЈжҺҘ

гҖҖгҖҖеӯҳе„І(chЗ”)еҷЁең°еқҖеҜ„еӯҳеҷЁпјҲMARпјүе’Ңеӯҳе„І(chЗ”)еҷЁж•ё(shГ№)ж“�(jГ№)еҜ„еӯҳеҷЁпјҲMDRпјүжҳҜдё»еӯҳе’ҢCPUд№Ӣй–“зҡ„жҺҘеҸ����гҖӮMARеҸҜд»ҘжҺҘеҸ—дҫ�(lГЎi)иҮӘзЁӢеәҸиЁҲ(jГ¬)ж•�(shГ№)еҷЁзҡ„жҢҮд»Өең°еқҖжҲ–дҫҶ(lГЎi)иҮӘең°еқҖеҪўжҲҗйғЁд»¶зҡ„ж“ҚдҪңж•ё(shГ№)ең°еқҖ���пјҢд»Ҙзўәе®ҡиҰҒиЁӘе•�(wГЁn)зҡ„е–®е…ғгҖӮMDRжҳҜеҗ‘дё»еӯҳеҜ�(xiДӣ)е…Ҙж•ё(shГ№)ж“�(jГ№)жҲ–еҫһдё»еӯҳи®ҖеҮәж•ё(shГ№)ж“�(jГ№)зҡ„з·©жІ–йғЁд»����гҖӮMARе’ҢMDRеҫһеҠҹиғҪдёҠзңӢеұ¬дәҺдё»еӯ����пјҢдҪҶеңЁе°ҸеһӢиЁҲ(jГ¬)з®—ж©ҹ(jД«)гҖҒеҫ®еһӢиЁҲ(jГ¬)з®—ж©ҹ(jД«)дёӯеёёж”ҫеңЁCPUе…�(nГЁi)�����гҖ�

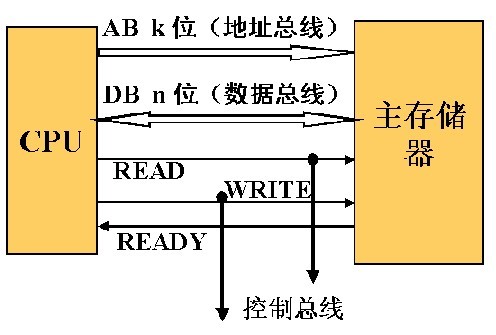

гҖҖгҖҖCPUиҲҮдё»еӯҳзҡ„зЎ¬йҖЈжҺҘжҳҜе…©еҖ�(gГЁ)йғЁд»¶д№Ӣй–“иҒ�(liГЎn)зі»зҡ„зү©зҗҶеҹәзӨҺ(chЗ”)пјҢе…·й«”е®ҢжҲҗи®ҖжҲ�?qЕ«)жҲҮвӮ¬йңҖиҰҒе…©еҖ�(gГЁ)йғЁд»¶д№Ӣй–“зҡ„и»ҹйҖЈжҺҘ���пјҢеҚіCPUеҗ‘дё»еӯҳзҷј(fДҒ)еҮәзҡ„и®ҖжҲ�?qЕ«)жҮЁоҸҢ?����пјҢйҖҷжүҚжҳҜе…©еҖ�(gГЁ)йғЁд»¶д№Ӣй–“жңүж•Ҳе·ҘдҪңзҡ„й—ң(guДҒn)йҚ������гҖӮи®ҖеҜ�(xiДӣ)зҡ„еҹәжң¬ж“ҚдҪңеҰӮдёӢпјҡ

гҖҖ?����гҖ�?пјүи®Җ�гҖӮи®Җж“ҚдҪңжҳҜжҢҮеҫһCPUйҖҒдҫҶ(lГЎi)зҡ„ең°еқҖжүҖжҢҮе®ҡзҡ„еӯҳе„�(chЗ”)е–®е…ғдёӯеҸ–еҮәдҝЎжҒ����пјҢеҶҚйҖҒзөҰCPU���пјҢе…¶ж“ҚдҪңйҒ�(guГІ)зЁӢеҰӮдёӢпјҡ

гҖҖгҖҖв‘� ең°еқҖвҶ’MARвҶ’ABпјҡCPUе°Үең°еқҖдҝЎиҷҹ(hГ o)йҖҒиҮіең°еқҖзёҪз·ҡ��пј�

гҖҖ?гҖ�?ReadпјҡCPUзҷ�(fДҒ)еҮәи®Җе‘Ҫд»Ө����пј�

гҖҖ?���гҖ�?Wait for MFCпјҡзӯүеҫ…еӯҳе„�(chЗ”)еҷЁе·ҘдҪңе®ҢжҲҗдҝЎиҷ�(hГ o)пј�

гҖҖ?��гҖ�?M(MAR)вҶ’DBвҶ’MDRпјҡи®ҖеҮәдҝЎжҒҜ經(jД«ng)ж•�(shГ№)ж“�(jГ№)зёҪз·ҡйҖҒиҮіCPUгҖ�

гҖҖ?����гҖ�?пјүеҜ«(xiДӣ)����гҖӮеҜ«(xiДӣ)ж“ҚдҪңжҳҜжҢҮе°ҮиҰҒеҜ�(xiДӣ)е…Ҙзҡ„дҝЎжҒҜеӯҳе…ҘCPUжүҖжҢҮе®ҡзҡ„еӯҳе„�(chЗ”)е–®е…ғдёӯпјҢе…¶ж“ҚдҪңйҒҺ(guГІ)зЁӢеҰӮдёӢпјҡ

гҖҖ?�гҖ�?ең°еқҖвҶ’MARвҶ’ABпјҡCPUе°Үең°еқҖдҝЎиҷҹ(hГ o)йҖҒиҮіең°еқҖзёҪз·ҡ���пј�

гҖҖ?��гҖ�?ж•�(shГ№)ж“�(jГ№)вҶ’MDRвҶ’DBпјҡCPUе°ҮиҰҒеҜ�(xiДӣ)е…Ҙзҡ„ж•�(shГ№)ж“�(jГ№)йҖҒиҮіж•�(shГ№)ж“�(jГ№)зёҪз·ҡпј�

гҖҖгҖҖв‘� WriteпјҡCPUзҷ�(fДҒ)еҮәеҜ«(xiДӣ)е‘Ҫд»Ө����пј�

гҖҖгҖҖв‘� Wait for MFCпјҡзӯүеҫ…еӯҳе„�(chЗ”)еҷЁе·ҘдҪңе®ҢжҲҗдҝЎиҷ�(hГ o)���гҖ�

гҖҖгҖҖз”ұдәҺCPUе’Ңдё»еӯҳзҡ„йҖҹеәҰеӯҳеңЁи‘—е·®и·����пјҢжүҖд»Ҙе…©иҖ…д№Ӣй–“зҡ„йҖҹеәҰеҢ№й…ҚжҳҜеҫҲй—�(guДҒn)йҚөзҡ„гҖӮйҖҡеёёжңүе…©зЁ®еҢ№й…Қж–№ејҸпјҡеҗҢжӯҘеӯҳе„І(chЗ”)еҷЁи®ҖеҸ–е’Ңз•°жӯҘеӯҳе„І(chЗ”)еҷЁи®ҖеҸ�����гҖӮдёҠйқўзөҰеҮәзҡ„и®ҖеҜ�(xiДӣ)еҹәжң¬ж“ҚдҪңжҳҜд»Ҙз•°жӯҘеӯҳе„І(chЗ”)еҷЁи®ҖеҸ–дҫҶ(lГЎi)иҖғж…®зҡ„пјҢCPUе’Ңдё»еӯҳд№Ӣй–“жІ’(mГ©i)жңүзөұ(tЗ’ng)дёҖзҡ„жҷӮ(shГӯ)йҗ����пјҢз”ұдё»еӯҳе·ҘдҪңе®ҢжҲҗдҝЎиҷҹ(hГ o)пјҲMFCпјүйҖҡзҹҘCPUвҖңдё»еӯҳе·ҘдҪңе·Іе®ҢжҲҗвҖ��гҖ�