гҖҖгҖҖжңүйҷҗй•·жІ–жҝҖйҹҝжҮү(FIR)жҝҫжіўеҷЁеңЁж•�(shГ№)еӯ—дҝЎиҷҹиҷ•зҗҶдёӯжҳҜдёҖзЁ®еҹәжң¬зҡ„иҷ•зҗҶе–®е…ғ��гҖӮз„Ўйҷҗй•·е–®дҪҚжІ–жҝҖйҹҝжҮү(IIR)ж•�(shГ№)еӯ—жҝҫжіўеҷЁзҡ„е„Ә(yЕҚu)й»һжҳҜеҸҜд»ҘеҲ©з”ЁжЁЎж“¬жҝҫжіўеҷЁиЁӯиЁҲзҡ„зөҗжһң�����пјҢдҪҶе…¶зјәй»һжҳҜдёҚе…·жңүз·ҡжҖ§зӣёдҪҚжҖ������гҖӮең–еғҸиҷ•зҗҶд»ҘеҸҠж•ё(shГ№)ж“�(jГ№)еӮіијёйғҪиҰҒжұӮдҝЎйҒ“е…·жңүз·ҡжҖ§зӣёдҪҚзү№жҖ������пјҢF(xiГ n)IRжҝҫжіўеҷЁеҸҜд»ҘеҒҡжҲҗеҡҙж јзҡ„з·ҡжҖ§зӣёдҪ������пјҢйҒҝе…Қиў«иҷ•зҗҶдҝЎиҷҹз”�(chЗҺn)з”ҹзӣёдҪҚеӨұзңҹпјҢйӮ„еҸҜд»Ҙе…·жңүд»»ж„Ҹзҡ„е№…еәҰзү№жҖ��гҖӮжӯӨеӨ–пјҢF(xiГ n)IRжҝҫжіўеҷЁзҡ„е–®дҪҚжІ–жҝҖйҹҝжҮүжҳҜжңүйҷҗй•·зҡ��пјҢеӣ иҖҢжҝҫжіўеҷЁдёҖе®ҡжҳҜз©�(wДӣn)е®ҡзҡ„гҖ�

гҖҖгҖҖеңЁж•ё(shГ№)еӯ—жҝҫжіўеҷЁзҡ„з ”з©¶дёӯ���пјҢе·Із¶�(jД«ng)жҸҗеҮәеӨҡзЁ®FIRжҝҫжіўеҷЁзҡ„иЁӯиЁҲе’ҢеҜҰзҸ�(xiГ n)ж–№жі•�����пјҢеҰӮ并иЎҢзөҗж§Ӣ��гҖҒжөҒж°ҙз·ҡзөҗж§Ӣ�гҖҒеҲҶеёғејҸзөҗж§Ӣзӯү[1-3]��гҖӮFIRжҝҫжіўеҷЁиЁҲз®—йҮҸеӨ�����пјҢдё”иҰҒжұӮеҜҰжҷӮеҜҰзҸҫ(xiГ n)гҖӮеҰӮдҪ•жҸҗй«ҳйҖҹеәҰд»Ҙж»ҝи¶ідҝЎиҷҹиҷ•зҗҶзҡ„й«ҳж•ҲжҖ§е’ҢеҜҰжҷӮжҖ§дёҖзӣҙжҳҜдәәеҖ‘з ”з©¶зҡ„йҮҚй»һе’ҢзҶұй»����гҖӮи„ҲеӢ•йҷЈеҲ—жҳҜдёҖзЁ®ж–°еһӢзҡ„жөҒж°ҙз·ҡзөҗж§������пјҢжүҖжңүиҷ•зҗҶе–®е…ғжҳҜзӣёеҗҢдё”е…ЁжөҒж°ҙзҡ����пјҢ并且жңүжЁЎеЎҠеҢ–е’ҢиҰ�(guД«)еүҮеҢ–зҡ„зү№еҫ����пјҢйҖҷе°ҚдәҺ硬件иЁӯиЁҲжҳҜеҫҲйҮҚиҰҒзҡ„����гҖӮи„ҲеӢ•йҷЈеҲ—зөҗж§ӢеҸҜд»ҘеҫҲеҘҪең°ж»ҝи¶ій«ҳйҖҹеҜҰжҷӮдҝЎиҷҹиҷ•зҗҶзҡ„йңҖиҰҒпјҢжҸҗй«ҳж•�(shГ№)ж“�(jГ№)зҡ„йҖҡйҒҺзҺҮеҸҠйӣ»и·Ҝзҡ„еҹ·(zhГӯ)иЎҢйҖҹеәҰ�гҖӮи©Ізөҗж§ӢзөҗеҗҲдәҶ并иЎҢзөҗж§Ӣе’ҢжөҒж°ҙз·ҡзҡ„е„�(yЕҚu)еӢўпјҢдҪҝFIRжҝҫжіўеҷЁйҒ”еҲ°дәҶжӣҙй«ҳзҡ„иҷ•зҗҶйҖҹеәҰ�гҖ�

гҖҖгҖҖж•�(shГ№)еӯ—жҝҫжіўеҷЁзҸ�(xiГ n)еңЁеӨ§еӨҡеңЁDSPиҠҜзүҮдёҠеҜҰзҸ�(xiГ n)[4]гҖӮйҡЁи‘—йӣҶжҲҗйӣ»и·ҜжҠҖиЎ“зҡ„зҷ�(fДҒ)еұ��пјҢзҸҫ(xiГ n)еңЁе·ІжңүеӨҡзЁ®е°Ҳз”ЁDSPиҠҜзүҮз”ЁдәҺеҜҰзҸҫ(xiГ n)жҝҫжіўгҖҒFFTзӯүйҒӢз®������гҖӮеҸҰеӨ������пјҢF(xiГ n)PGAе…�(nГЁi)йғЁзҡ„иҰ�(guД«)ж•ҙзҡ„йӮҸијҜеЎҠйҷЈеҲ—пјҢеҫҲйҒ©еҗҲеҜҰзҸ�(xiГ n)и„ҲеӢ•йҷЈеҲ—йҖҷзЁ®й«ҳеәҰ并иЎҢзҡ„йҒӢз®������гҖӮAlteraе…¬еҸёж–°жҺЁеҮәзҡ„Stratixзі»еҲ—FPGAе…�(nГЁi)йғЁжңүиұҗеҜҢзҡ„йӮҸијҜйҷЈеҲ—иіҮжәҗеҸҠй«ҳжҖ§иғҪеөҢе…ҘејҸDSPеЎ��пјҢиғҪеӨ й«ҳж•Ҳең°еҜҰзҸҫ(xiГ n)ж•�(shГ№)еӯ—дҝЎиҷҹиҷ•зҗҶеҠҹиғҪ[5]гҖ�

гҖҖгҖҖжң¬ж–ҮйҰ–е…Ҳд»Ӣзҙ№дәҶFIRжҝҫжіўеҷЁе’Ңи„ҲеӢ•йҷЈеҲ—зҡ„еҺҹзҗ����пјҢ然еҗҺиЁӯиЁҲдәҶи„ҲеӢ•йҷЈеҲ—зөҗж§Ӣзҡ„FIRжҝҫжіўеҷ����пјҢз•«еҮәйӣ»и·Ҝзҡ„зөҗж§ӢжЎҶең–пјҢ并йҖІиЎҢдәҶжҷӮеәҸеҲҶжһ��пјҢеңЁFPGAдёҠйҖІиЎҢй©—иӯүгҖӮзөҗжһңиЎЁжҳ����пјҢи„ҲеӢ•йҷЈеҲ—зҡ„жЁЎеЎҠеҢ–е’Ңй«ҳеәҰжөҒж°ҙз·ҡзҡ„зөҗж§ӢдҪҝFIRжҝҫжіўеҷЁеңЁFPGAдёҠзҚІеҫ—дәҶеҫҲеҘҪзҡ„жҖ§иғҪ��пјҢжҜ”дёІиЎҢзөҗж§Ӣзҡ„йҒӢз®—йҖҹеәҰжӣҙеҝ«��пјҢе‘өд»ҘжӣҙеҘҪең°ж»ҝи¶іж•�(shГ№)еӯ—дҝЎиҷҹиҷ•зҗҶдёӯй«ҳж•Ҳ�����гҖҒеҜҰжҷӮзҡ„иҰҒжұӮ���гҖ�

гҖҖгҖҖ2 FIRжҝҫжіўеҷЁеҸҠи„ҲеӢ•йҷЈеҲ—еҺҹзҗҶ

гҖҖгҖҖ2.1 FIRжҝҫжіўеҷЁеҺҹзҗ�

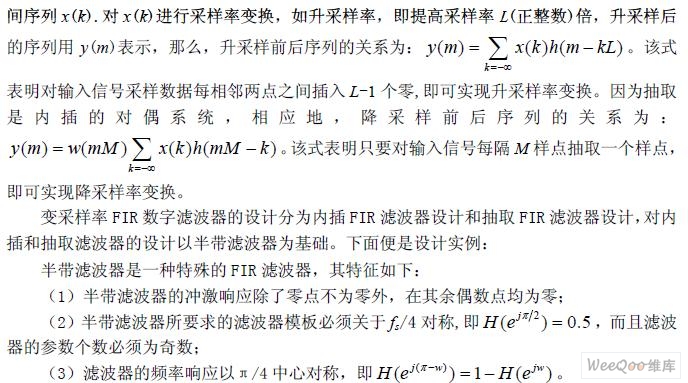

гҖҖгҖҖж•�(shГ№)еӯ—жҝҫжіўеҷЁз”ЁдәҺж”№и®Ҡијёе…ҘдҝЎиҷҹX(n)зҡ„й »иӯңзү№жҖ§д»Ҙж»ҝи¶іжҹҗзЁ®зү№е®ҡзҡ„иЁӯиЁҲиҰҒжұ����гҖӮдёҖеҖӢеӣ жһңзҡ„ж•�(shГ№)еӯ—жҝҫжіўеҷЁеҸҜд»Ҙз”Ёе®ғзҡ„е–®дҪҚжІ–жҝҖйҹҝжҮүh(n)гҖҒеӮіијёеҮҪж•�(shГ№)H(z)жҲ–иҖ…е·®еҲҶж–№зЁӢдҫҶиЎЁйҒ”��гҖӮе…¶дёӯе–®дҪҚжІ–жҝҖйҹҝжҮүе’ҢеӮіијёеҮҪж•�(shГ№)жҸҸиҝ°дәҶзі»зө�(tЗ’ng)зҡ„жҷӮеҹҹе’Ңй »еҹҹжҖ§иіӘ�����пјҢе·®еҲҶж–№зЁӢеүҮеҸҚжҳ дәҶеҜҰзҸ�(xiГ n)и©ІжҝҫжіўеҷЁжүҖйңҖзҡ„йҒӢз®�����гҖ�

гҖҖгҖҖдёҖеҖӢз·ҡжҖ§жҷӮдёҚи®Ҡеӣ жһңжҝҫжіўеҷЁеҸҜд»Ҙз”Ёеј�(1)зҡ„е·®еҲҶж–№зЁӢжҸҸиҝ°пјҡ

гҖҖгҖҖеҰӮжһң1вүӨkвүӨNжҷ����пјҢak=0����пјҢеүҮпј�

гҖҖгҖҖйҖҷе°ұжҳҜдёҖеҖӢMйҡҺзҡ„FIRжҝҫжіўеҷ������пјҢжҳҜйқһйҒһжӯёйҒӢз®�����гҖ�

гҖҖгҖҖ2.2 и„ҲеӢ•йҷЈеҲ—

гҖҖгҖҖи„ҲеӢ•йҷЈеҲ—зөҗж§Ӣжҳ�1978е№ҙз”ұCarneige-MellonеӨ§еӯёзҡ„H.T.Kungзӯүдәәзҷ�(fДҒ)еұ•иө·дҫҶзҡ„дёҖзЁ®е°Ҳз”Ёиҷ•зҗҶеҷЁиЁӯиЁҲжЁЎеһӢ�пјҢжҳҜдёҖзЁ®ж–°зҡ„жөҒж°ҙз·ҡзөҗж§Ӣ��пјҢиЎЁзӨәдёҖзЁ®жңүзҜҖ(jiГ©)еҘҸең°жұҒ算并йҖҡйҒҺзі»зөұ(tЗ’ng)еӮіијёж•�(shГ№)ж“�(jГ№)зҡ„иҷ•зҗҶе–®е…ғз¶І(wЗҺng)зө��гҖӮйҖҷдәӣиҷ•зҗҶе–®е…ғиҰ�(guД«)еүҮең°жіөе…ҘжіөеҮәж•�(shГ№)ж“�(jГ№)д»Ҙз¶ӯжҢҒиҰҸ(guД«)еүҮзҡ„ж•�(shГ№)ж“�(jГ№)жөҒ[6]гҖӮз”ұдәҺе…¶ж•�(shГ№)ж“�(jГ№)йҒӢз®—иҲҮеӮійҖҒж–№ејҸйЎһдјјдәҺеҝғиҮҹжҲ–и„ҲжҗҸжңүзҜҖ(jiГ©)еҘҸең°и·іеӢ•����пјҢеӣ жӯӨиў«зЁұзӮәеҝғеӢ•йҷЈеҲ—жҲ–и„ҲеӢ•йҷЈеҲ—гҖӮеҲ©з”Ёи„ҲеӢ•йҷЈеҲ—еҸҜиЁӯиЁҲеҮәдёҖзі»еҲ—йҒ©еҗҲж•�(shГ№)еӯ—дҝЎиҷҹиҷ•зҗҶжҮүз”Ёзҡ„жЁЎеЎҠеҢ������гҖҒиҰҸ(guД«)еүҮдё”жңүж•Ҳзҡ„йҒӢз®—зөҗж§������гҖӮи„ҲеӢ•йҷЈеҲ—зөҗж§Ӣзҡ„еҹәжң¬зү№жҖ§еҰӮдёӢпјҡ

гҖҖгҖҖ(1)и„ҲеӢ•жҖ�

гҖҖгҖҖж•�(shГ№)ж“�(jГ№)еңЁдёҖеҖӢе…ЁеұҖжҷӮйҗҳзҡ„зІҫзўәжҺ§еҲ¶дёӢ����пјҢжңүзҜҖ(jiГ©)еҘҸең°з¶�(jД«ng)йҒҺиЁҲз®—е’ҢеӮійҒһйҒҺзЁӢпјҢйҖҡйҒҺз¶�(wЗҺng)зө���гҖ�

гҖҖгҖҖ(2)жЁЎеЎҠжҖ§е’ҢиҰ�(guД«)еүҮжҖ�

гҖҖгҖҖйҷЈеҲ—з”ұжЁЎеЎҠеҢ–зҡ„иҷ•зҗҶе–®е…ғзө„жҲ����пјҢеҗ„иҷ•зҗҶе–®е…ғд№Ӣй–“зҡ„дә’йҖЈж–№ејҸеқҮеӢ»дёҖиҮ����пјҢ并且иЁҲз®—з¶І(wЗҺng)зөЎеҸҜд»»ж„Ҹж“ҙеӨ§����гҖ�

гҖҖгҖҖ(3)з©әй–“еұҖйғЁжҖ§е’ҢжҷӮй–“еұҖйғЁжҖ�

гҖҖгҖҖиЎЁзҸҫ(xiГ n)еңЁж•ё(shГ№)ж“�(jГ№)еҫһдёҖеҖӢиЁҲз®—зҜҖ(jiГ©)й»һеӮійҒһеҲ°дёӢдёҖеҖӢиЁҲз®—зҜҖ(jiГ©)й»һиҮіе°‘йңҖиҰҒдёҖеҖӢе–®е…ғжҷӮй–����гҖ�

гҖҖгҖҖ(4)жңүж•Ҳзҡ„жөҒж°ҙз·ҡзөҗж§Ӣ

гҖҖгҖҖи„ҲеӢ•йҷЈеҲ—е…ҚйҷӨдәҶеҪўжҲҗж•ё(shГ№)ж“�(jГ№)жөҒжүҖйңҖзҡ„жҺ§еҲ¶й–ӢйҠ���гҖӮйҷЈеҲ—е…§(nГЁi)иҷ•зҗҶе–®е…ғй–“зҡ„еұҖйғЁйҖЈжҺҘж–№ејҸдҪҝйҷЈеҲ—дёӯиІ ијүеқҮеӢ»�����гҖҒйҖЈз·ҡжҘөзҹӯ�����пјҢйҷҗеәҰең°жёӣе°ҸдәҶзі»зө�(tЗ’ng)е…�(nГЁi)йғЁзҡ„йҖҡдҝЎе»¶жҷӮпјҢжҸҗй«ҳдәҶиҷ•зҗҶе–®е…ғзҡ„еҲ©з”ЁзҺҮ����пјҢдҪҝж•ҙеҖӢйҷЈеҲ—зҡ„зі»зөұ(tЗ’ng)жҖ§иғҪеҫ—еҲ°е……еҲҶзҷ�(fДҒ)жҸ®гҖ�

гҖҖгҖҖи„ҲеӢ•зөҗж§ӢжҳҜе°Үз·ҡжҖ§жҳ е°„жҠҖиЎ“з”ЁдәҺиҰҸ(guД«)еүҮдҫқиіҙең–дёҠйҖІиЎҢиЁӯиЁҲзҡ����гҖӮдҫқиіҙең–зҡ„йӮҠиЎЁзӨәе„�(yЕҚu)е…Ҳзҙ„жқ����гҖӮи„ҲеӢ•йҷЈеҲ—иЁӯиЁҲдёӯзҡ„еҹәжң¬зҹўйҮҸжңүпј�

гҖҖгҖҖ(1)жҠ•еҪұзҹўйҮҸпј�

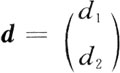

гҖҖгҖҖ(2)иҷ•зҗҶеҷЁзҹўйҮҸпјҡPT=(p1 p2)

гҖҖгҖҖ(3)иӘҝеәҰзҹўйҮҸпјҡST=(S1 S2)

гҖҖгҖҖ(4)硬件еҲ©з”ЁзҺҮпјҡHUE=1/в”ӮSTd в”�

гҖҖгҖҖ3 FlRжҝҫжіўеҷЁзҡ„и„ҲеӢ•зөҗж§ӢиЁӯиЁҲ

гҖҖгҖҖ3.1 FIRжҝҫжіўеҷЁзҡ„и„ҲеӢ•йҷЈеҲ—зөҗж§Ӣ

гҖҖгҖҖз”ЁиӘҝеәҰдёҚзӯүејҸйҒёж“ҮеҸҜиЎҢзҡ„иӘҝеәҰзҹўйҮҸST��пјҢе№¶ж №ж“ҡ(jГ№)и„ҲеӢ•зөҗж§Ӣзҡ„еҸҜиЎҢжҖ§йҷҗеҲ¶жўқ件йҒёж“ҮжҠ•еҪұзҹўйҮҸdе’Ңиҷ•зҗҶеҷЁз©әй–“зҹўйҮҸPT�пјҢ然еҗҺз”Ёз·ҡжҖ§жҳ е°„жҠҖиЎ“иЁӯиЁҲи„ҲеӢ•еҲ—�����гҖ�

гҖҖгҖҖйҒёж“ҮжҠ•еҪұзҹўйҮҸ����гҖҒиҷ•зҗҶеҷЁзҹўйҮҸе’ҢиӘҝеәҰзҹўйҮҸеҰӮдёӢпјҡ

гҖҖгҖҖдәҺжҳҜпјҢзҜҖ(jiГ©)й»һIT=(i��пјҢj)иў«иҷ•зҗҶзӮәпј�

гҖҖгҖҖзҜҖ(jiГ©)й»һIT=(i�пјҢj)зҡ„еҹ·(zhГӯ)иЎҢжҷӮй–“зӮәпј�

гҖҖгҖҖ硬件еҲ©з”ЁзҺҮпјҡ

гҖҖгҖҖд»Ҙдә”йҡҺFIRжҝҫжіўеҷЁзӮәдҫӢпјҡ

гҖҖгҖҖе…¶дёӯпјҢd0,d1�����пјҢd2е’Ңd3дҪңзӮә延жҷӮе–®е…ғ����пјҢm0�пјҢm1�пјҢвҖҰпјҢm4зӮәеӣәе®ҡд№ҳж•�(shГ№)зҡ„д№ҳжі•еҷЁ���пјҢд№ҳж•�(shГ№)еҲҶеҲҘзӮәП�0��пјҢП�1����пјҢвҖ��пјҢП�4гҖӮд№ҳжі•еҷЁm0е’ҢеҠ жі•еҷЁa0ж§ӢжҲҗиҷ•зҗҶеҷЁP0;д№ҳжі•еҷЁm1е’ҢеҠ жі•еҷЁa1ж§ӢжҲҗиҷ•зҗҶеҷЁP1;йЎһдјјзҡ������пјҢm4е’Ңa4ж§ӢжҲҗиҷ•зҗҶеҷЁP4�����гҖ�5еҖӢиҷ•зҗҶеҷЁеҗҢжҷӮе·ҘдҪң���пјҢx(n)ијёе…ҘеҗҺеҗҢжҷӮеҲ°йҒ�5еҖӢиҷ•зҗҶеҷЁпјҢеҲҶеҲҘе’Ңж¬ҠйҮҚПүiзӣёд№ҳеҗ����пјҢ經(jД«ng)дёҚеҗҢзҡ„延жҷӮзӣёеҠ еҫ—еҲ°зөҗжһңy(n)����гҖ�

гҖҖгҖҖи©ІиЁӯиЁҲжЎҶең–еҫҲеҘҪең°й«”зҸҫ(xiГ n)дә�2.2зҜҖ(jiГ©)жҸҗеҲ°зҡ„и„ҲеӢ•йҷЈеҲ—зҡ„4еҖӢеҹәжң¬зү№жҖ§гҖӮж•ё(shГ№)ж“�(jГ№)еңЁз¶І(wЗҺng)зөЎдёӯжңүзҜҖ(jiГ©)еҘҸзҡ„ијёе…Ҙ����гҖҒиЁҲз®—гҖҒеӮійҒһ并輸еҮә����гҖ�

гҖҖгҖҖи©Ізөҗж§Ӣз”ұ5еҖӢзӣёеҗҢзҡ„жЁЎеЎҠеҢ–иҷ•зҗҶеҷЁж§ӢжҲҗпјҢе®№жҳ“ж“ҙеұ������пјҢеҸҜеҜҰзҸҫ(xiГ n)д»»ж„ҸйҡҺзҡ„FIRжҝҫжіўеҷ���гҖӮж•ё(shГ№)ж“�(jГ№)зҡ„ијёе…���гҖҒе’Ңж¬ҠйҮҚзҡ„зӣёд№��гҖҒдёӯй–“зөҗжһңзҡ„еҜ„еӯҳгҖҒж•ё(shГ№)ж“�(jГ№)зҡ„ијёеҮәеҗ„йңҖиҰҒдёҖеҖӢе–®е…ғжҷӮе•�����пјҢдҪҶйҖҷе№ҫзЁ®ж“ҚдҪңеҸҜеҗҢжҷӮйҖІиЎҢ����пјҢдёҚжңғдә’зӣёе№Іж“��гҖӮи©Іи„ҲеӢ•йҷЈеҲ—зөҗж§Ӣд»Ҙй«ҳеәҰзҡ„жөҒж°ҙз·ҡж–№ејҸйҒӢиЎҢгҖ�

гҖҖгҖҖйңҖиҰҒжіЁж„Ҹзҡ„жҳ��пјҢеңЁд№ҳжі•еҷЁијёеҮәзҡ„жҷӮеҖҷйңҖиҰҒе°ҚијёеҮәзҡ„ж•ё(shГ№)ж“�(jГ№)йҖІиЎҢдёҖдҪҚж“ҙеұ•пјҢд»ҘйҒҝе…ҚеҠ жі•еҷЁзҡ„жәўеҮәе•ҸйЎ�����гҖ�

гҖҖгҖҖ3.2 жҷӮеәҸеҲҶжһҗ

гҖҖгҖҖи©Ізөҗж§Ӣзҡ„з©әе•ҸжҷӮй–“иЎЁзӨәеҰӮең–2жүҖзӨәгҖӮж©«и»ёзӮәжҷӮй–“и»���пјҢзёұи»ёзӮәиҷ•зҗҶеҷЁи»ё��гҖӮең–дёӯзҡ„жҜҸдёҖиЎҢе°ҚжҮүдёҖеҖӢиҷ•зҗҶеҷЁ�����?����пјҹжўўй’Ҙеҗ№зҡҶи·Ғrй–“и»ёзҡ„жҹҗдёҖй»һдёҠ���пјҢијёе…Ҙж•ё(shГ№)ж“�(jГ№)x(n)еңЁеҗҢдёҖжҷӮй–“еҠҚйҒ”жүҖжңүиҷ•зҗҶеҷЁ��пјҢеҚіијёе…Ҙ"е»Јж’ӯ";еңЁиҷ•зҗҶеҷЁи»ёзҡ„жҹҗдёҖй»һдёҠ�����пјҢж¬ҠйҮҚПүiеңЁеҗ„иҷ•зҗҶеҷЁдёӯиҷ•дәҺзӣёеҗҢзҡ„з©әй–“еқҗжЁ��пјҢеӣ жӯӨж¬ҠйҮ�"дҝқжҢҒ";иҖҢијёеҮәж•ё(shГ№)ж“�(jГ№)y(n)еңЁдёҚеҗҢзҡ„з©әй–“е’ҢжҷӮй–“еҫ—еҲ�����пјҢжүҖд»ҘијёеҮ�"移еӢ•"гҖӮи©ІFIRжҝҫжіўеҷЁзӮәијёе…Ҙе»Јж’ӯ����гҖҒж¬ҠйҮҚдҝқжҢҒгҖҒијёеҮә移еӢ•еһӢзҡ„и„ҲеӢ•йҷЈеҲ—зөҗж§���гҖ�

гҖҖгҖҖеҖҹеҠ©дәҺи„ҲеӢ•йҷЈеҲ—жҠҖиЎ����пјҢијёе…Ҙе’ҢијёеҮәд№Ӣй–“зҡ„иҷ•зҗҶеҸҜд»ҘеҗҢжҷӮйҖІиЎҢ���пјҢеӣ жӯӨпјҢзёҪзҡ„еҹ�(zhГӯ)иЎҢжҷӮй–“и®Ҡеҫ—жңҖе°����гҖӮе°Қи©Ізөҗж§ӢйҖІиЎҢжҷӮеәҸеҲҶжһҗ���пјҢеҰӮең�3жүҖзӨ������гҖӮеңЁеҖӢжҷӮйҗҳе‘Ёжңҹx(0)йҖҒеҲ°еҗ„иҷ•зҗҶеҷЁ��пјҢе’Ңж¬ҠйҮҚеҲҶеҲҘзӣёд№ҳеҗҺеңЁз¬¬дәҢеҖӢжҷӮйҗҳе‘Ёжңҹеҫ—еҲ°y(tЗ’ng)(0)=Пү0x(0)��пјҢеңЁжӯӨеҗҢжҷӮж•ё(shГ№)ж“�(jГ№)x(1)已經(jД«ng)ијёе…Ҙ;第дёүеҖӢжҷӮйҗҳе‘Ёжңҹијёе…Ҙx(2)���пјҢеңЁиҷ•зҗҶеҷЁP0еҫ—еҲ°Пү0x(1)пјҢжӯӨжҷӮиҷ•зҗҶеҷЁP1зҡ„зөҗжһңП�1x(0)з¶�(jД«ng)дёҖзҙҡ延жҷӮеҗҺе’ҢP0зҡ„зөҗжһңзӣёеҠ еҫ—еҲ°y(tЗ’ng)(1)=Пү0(1)+Пү1x(O)����гҖӮеҗҢзҗҶпјҢ第еӣӣеҖӢе‘Ёжңҹеҫ—еҲ°y(tЗ’ng)(2)=Пү0x(2)+Пү1x(1)+Пү2x(0)����пјҢ第дә”еҖӢе‘Ёжңҹеҫ—еҲ°y(tЗ’ng)(3)=Пү0x(3)+Пү1x(2)+Пү2x(1)+Пү3x(O)вҖҰгҖ�

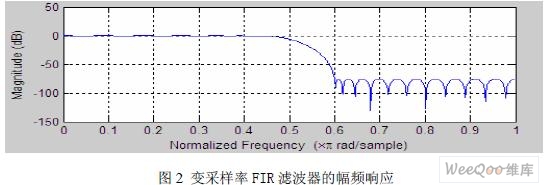

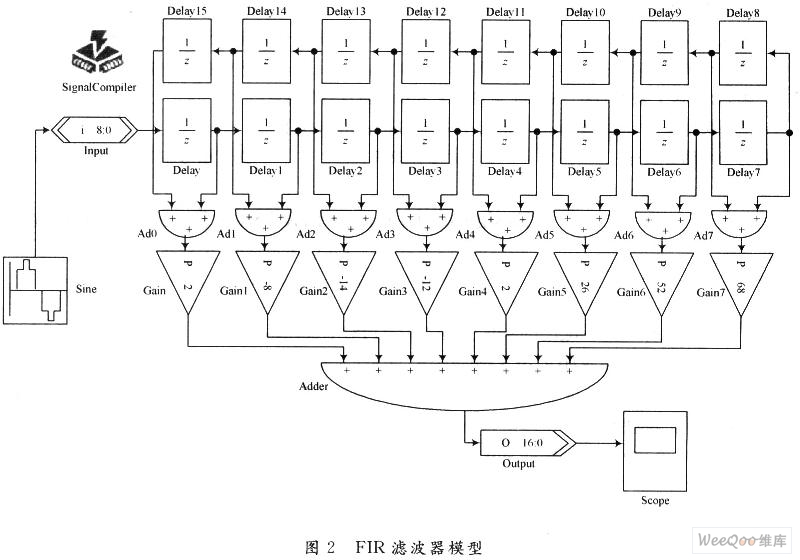

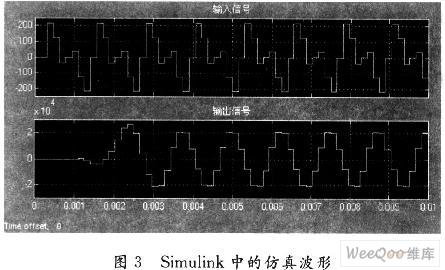

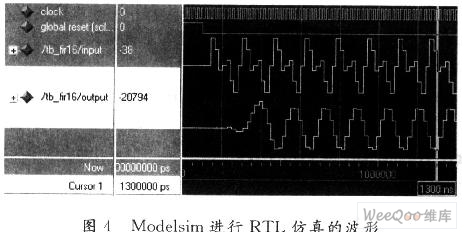

гҖҖгҖҖ4 FPGAй©—иӯү

гҖҖгҖҖд»ҘдёҖеҖӢијёе…ҘијёеҮәеқҮзӮ�8 bзҡ„дә”йҡҺFIRжҝҫжіўеҷЁзӮәдҫ����пјҢе°Қи©Іи„ҲеӢ•йҷЈеҲ—зөҗж§Ӣзҡ„FIRжҝҫжіўеҷЁеңЁFPGAдёҠйҖІиЎҢй©—иӯү����гҖӮзӣ®жЁҷеҷЁд»¶йҒёз”ЁStratixзі»еҲ—еҷЁд»¶пјҢз·ЁиӯҜи»ҹ件зӮәQuartusв…�4.2��гҖ�

гҖҖгҖҖStratixзі»еҲ—еҷЁд»¶жҳҜAlteraе…¬еҸёжҺЁеҮәзҡ„ж–°еһӢFPGA��пјҢе…¶е…�(nГЁi)йғЁжңүиұҗеҜҢзҡ„еөҢе…ҘејҸеӯҳе„Іеҷ����гҖҒе„Ә(yЕҚu)еҢ–зҡ„ж•�(shГ№)еӯ—дҝЎиҷҹиҷ•зҗ�(DSP)еЎҠе’Ңй«ҳжҖ§иғҪI/OиғҪеҠӣгҖӮStratixеҷЁд»¶жҳҜиЁӯиЁҲеҫ©йӣңзҡ„й«ҳжҖ§иғҪзі»зөұ(tЗ’ng)зҡ„зҗҶжғійҒёж“���гҖӮStratiXеҷЁд»¶дҪҝз”ЁDSPеЎҠеҜҰзҸ�(xiГ n)еӨ§иЁҲз®—йҮҸжҮүз”ЁжүҖйңҖзҡ„еӨ§ж•�(shГ№)ж“�(jГ№)еҗһеҗҗйҮ����гҖӮDSPеЎҠз”ұ硬件д№ҳжі•еҷ����гҖҒеҠ жі•еҷЁгҖҒжёӣжі•еҷЁ��гҖҒзҙҜеҠ еҷЁе’ҢжөҒж°ҙз·ҡеҜ„еӯҳеҷЁзө„жҲҗ[6]�гҖӮеҫһең�1дёӯеҸҜд»ҘзңӢеҮәпјҢжҜҸеҖӢиҷ•зҗҶеҷЁе–®е…ғз”ұдёҖеҖӢд№ҳжі•еҷЁе’ҢдёҖеҖӢеҠ жі•еҷЁж§ӢжҲҗ��пјҢйҖҷзЁ®зөҗж§ӢеҫҲйҒ©еҗҲз”ЁFPGAе…�(nГЁi)йғЁзҡ„DSPеЎҠеҜҰзҸ�(xiГ n)����гҖ�

гҖҖгҖҖеҜҰй©—зөҗжһңеҰӮиЎЁ1жүҖзӨ���гҖӮзӮәдәҶдҫҝдәҺжҜ”иј���пјҢдҪҝз”ЁзӣёеҗҢзҡ„еҷЁд»¶��пјҢйӮ„зөҰеҮәдәҶдёІиЎҢзөҗж§ӢFIRжҝҫжіўеҷЁзҡ„еҜҰй©—зөҗжһң���гҖӮеңЁдёІиЎҢзөҗж§ӢдёӯпјҢжҜҸж¬ЎиЁҲз®—1еҖӢx(n)���пјҢйңҖиҰ�3еҖӢжҷӮйҗҳе‘Ёжң���гҖӮи„ҲеӢ•йҷЈеҲ—зөҗж§ӢжҜҸж¬ЎиЁҲз®�5еҖӢx(n)���пјҢйңҖиҰ�5еҖӢжҷӮйҗҳе‘ЁжңҹгҖӮжҜҸеҖӢx(n)зӮ�8 bж•�(shГ№)ж“�(jГ№)��гҖӮйҒӢз®—йҖҹеәҰеҸҜд»Ҙз”ұдёӢйқўзҡ„е…¬ејҸеҫ—еҮәпј�

гҖҖгҖҖйҒӢз®—йҖҹеәҰ=(жҜҸж¬Ўиҷ•зҗҶж•�(shГ№)ж“�(jГ№)й•·еәҰ/йҒӢз®—иҖ—з”Ёзҡ„жҷӮйҗҳе‘Ёжңҹж•ё(shГ№))Г—зі»зөұ(tЗ’ng)жҷӮйҗҳй »зҺҮ

гҖҖгҖҖеҫһиЎЁдёӯеҸҜд»ҘзңӢеҮ����пјҢеңЁеҚ з”ЁйӮҸијҜе–®е…ғзҡ„ж•ё(shГ№)йҮҸдёҠдәҢиҖ…еҹәжң¬зӣёз•�����пјҢйӣ–然串иЎҢзөҗж§ӢеҸӘеҚ з”ЁдәҶдёҖеҖӢDSPеЎҠпјҢи„ҲеӢ•йҷЈеҲ—зөҗж§ӢеҚ з”Ёдә�5еҖ����пјҢдҪҶдёІиЎҢзөҗж§Ӣзҡ„йҒӢз®—йҖҹеәҰеҸӘиғҪйҒ”еҲ°284.93 Mb/s�����пјҢи„ҲеӢ•йҷЈеҲ—еҸҜд»ҘйҒ”еҲ�1 840.32 Mb/s�����гҖӮйЎҜ然и„ҲеӢ•йҷЈеҲ—зөҗж§Ӣжӣҙе…·е„Ә(yЕҚu)еӢўпјҢеҸҜд»ҘжӣҙеҘҪең°ж»ҝи¶іж•ё(shГ№)еӯ—дҝЎиҷҹиҷ•зҗҶдёӯй«ҳж•Ҳ���гҖҒеҜҰжҷӮзҡ„иҰҒжұӮ�гҖӮжң¬ж–ҮеҹәдәҺи„ҲеӢ•йҷЈеҲ—жҠҖиЎ������пјҢиЁӯиЁҲдәҶй«ҳж•Ҳзҡ„FIRжҝҫжіўеҷ���пјҢе…·жңүжЁЎеЎҠеҢ–е’ҢжөҒж°ҙз·ҡзҡ„зөҗж§�����пјҢ并充еҲҶеҲ©з”ЁдәҶFPGAиіҮжәҗ����пјҢйҒ”еҲ°дәҶијғй«ҳзҡ„е·ҘдҪңй »зҺ����гҖ�

гҖҖгҖҖ5 зө� иӘ�

гҖҖгҖҖFIRжҝҫжіўеҷЁжҳҜж•�(shГ№)еӯ—дҝЎиҷҹиҷ•зҗҶдёӯзҡ„дёҖзЁ®еҹәжң¬йҒӢз®��пјҢжңүи‘—е»Јжіӣзҡ„жҮүз”Ё����гҖӮеҹәдәҺи„ҲеӢ•йҷЈеҲ—зөҗж§������пјҢжң¬ж–ҮиЁӯиЁҲдәҶй«ҳж•Ҳзҡ„FIRжҝҫжіўеҷ������гҖӮжЁЎеЎҠеҢ–е’Ңй«ҳеәҰжөҒж°ҙз·ҡзҡ„зөҗж§ӢдҪҝеҫ—е…¶еңЁFPGAдёҠзҚІеҫ—дәҶијғеҘҪзҡ„жҖ§иғҪ�пјҢе®Ңе…ЁеҸҜд»Ҙж»ҝи¶ізі»зө�(tЗ’ng)й«ҳж•ҲгҖҒеҜҰжҷӮиҷ•зҗҶзҡ„иҰҒжұӮ��пјҢжҸҗй«ҳдәҶзі»зөұ(tЗ’ng)йҒӢз®—йҖҹеәҰ并充еҲҶеҗҲзҗҶең°еҲ©з”ЁдәҶFPGAиіҮжәҗ�гҖӮеҸҰеӨ–пјҢз”ұдәҺи„ҲеӢ•йҷЈеҲ—иҮӘиә«зҡ„зү№й»һпјҢеҗ„зҙҡзөҗж§ӢзӣёеҗҢ�����пјҢж–№дҫҝж“ҙеұ���пјҢеҸҜд»ҘеҜҰзҸ�(xiГ n)д»»ж„ҸйҡҺзҡ„FIRжҝҫжіўеҷ����гҖ�