дәӨйҢҜзҡ„еўҠ

й«ҳйҒ”3.2 Gb/s

зҶұжҸ’жӢ”еҗҲиҰ�(guД«)жҖ�

е°ҲзӮәдҪҺжҲҗжң¬иҖҢиЁӯ(shГЁ)иЁ�

еӨҡеҖӢй«ҳж•Ҳзҡ„йӣҶжҲҗеЎ�

е„�(yЕҚu)еҢ–зҡ„I/OжЁ�(biДҒo)жә�(zhЗ”n)йҒёж“Ү

еӨ§жү№йҮҸеЎ‘ж–ҷз·ҡз„ҠеҢ…иЈ�

йқңж…Ӣ(tГ i)е’ҢеӢ•ж…�(tГ i)еҠҹзҺҮдҪ�

дј‘зң жҺүйӣ»жЁЎејҸ��пјҢеҜҰзҸ�(xiГ n)йӣ¶еҠҹиҖ�

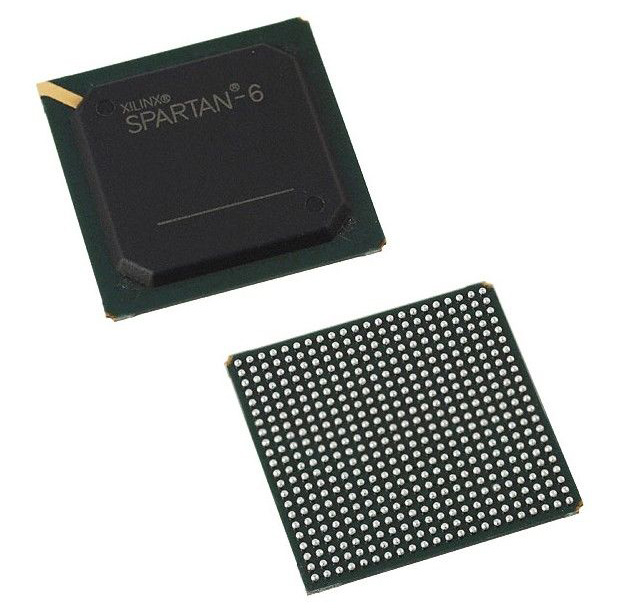

Spartan-6 LX FPGAпјҡйӮҸијҜе„Ә(yЕҚu)еҢ�

45зҙҚзұіе·Ҙи—қйҮқе°ҚжҲҗжң¬е’ҢдҪҺеҠҹиҖ—йҖІиЎҢдәҶе„Ә(yЕҚu)еҢ�

еӨҡйӣ»еЈ������пјҢеӨҡжЁ�(biДҒo)жә�(zhЗ”n)SelectIO?жҺҘеҸЈзө�

жҜҸеҖӢе·®еҲҶI/Oзҡ„ж•ё(shГ№)ж“�(jГ№)еӮіијёйҖҹзҺҮй«ҳйҒ”1,080 Mb/s

еҸҜйҒёијёеҮәй©�(qЕ«)еӢ����пјҢжҜҸеҖӢеј•и…іжңҖй«�24 mA

3.3VиҮ�1.2VI/OжЁ�(biДҒo)жә�(zhЗ”n)е’ҢеҚ”(xiГ©)иӯ�

дҪҺжҲҗжң¬HSTLе’ҢSSTLеӯҳе„ІеҷЁжҺҘеҸ�

еҸҜиӘҝ(diГ o)зҜҖ(jiГ©)зҡ„I/OиҪ�(zhuЗҺn)жҸӣйҖҹзҺҮеҸҜжҸҗй«ҳдҝЎиҷҹе®Ңж•ҙжҖ�

LXT FPGAдёӯзҡ„й«ҳйҖҹGTPдёІиЎҢ收зҷј(fДҒ)еҷ�

з”ЁдәҺPCI ExpressиЁ�(shГЁ)иЁҲзҡ„йӣҶжҲҗз«Ҝй»һжЁЎеЎҠ(LXT)

дҪҺжҲҗжң¬PCI?жҠҖиЎ�(shГ№)ж”ҜжҢҒе…је®№33 MHz���пј�32дҪҚе’Ң64дҪҚиҰҸ(guД«)иҢ��гҖ�

й«ҳж•Ҳзҡ„DSP48A1еҲҮзүҮ

й«ҳжҖ§иғҪз®—иЎ“(shГ№)е’ҢдҝЎиҷҹиҷ•зҗ�

еҝ«йҖ�18 x 18д№ҳжі•еҷЁе’Ң48дҪҚзҙҜеҠ еҷЁ

жөҒж°ҙз·ҡе’ҢзҙҡиҒҜ(liГЎn)еҠҹиғҪ

й �(yГ№)еҠ жі•еҷЁд»ҘеҚ�(xiГ©)еҠ©йҒҺжҝҫеҷЁжҮ�(yД«ng)з”ЁзЁӢеә�

йӣҶжҲҗе…�(nГЁi)еӯҳжҺ§еҲ¶еҷЁеЎ�

DDR����пјҢDDR2пјҢDDR3е’ҢLPDDRж”ҜжҢҒ

ж•�(shГ№)ж“�(jГ№)йҖҹзҺҮй«ҳйҒ”800 Mb/s(еі°еҖјеё¶еҜ¬зӮә12.8 Gb/s)

е…·жңүзҚЁз«ӢFIFOзҡ„еӨҡз«ҜеҸЈзёҪз·ҡзө�(jiГ©)ж§�(gГІu)еҸҜжёӣе°‘иЁӯ(shГЁ)иЁҲжҷӮеәҸе•ҸйЎ�

иұҗеҜҢзҡ„йӮҸијҜиіҮжәҗе’Ңжӣҙй«ҳзҡ„йӮҸијҜе®№йҮ�

еҸҜйҒёзҡ„移дҪҚеҜ„еӯҳеҷЁжҲ–еҲҶеёғејҸRAMж”ҜжҢҒ

й«ҳж•Ҳзҡ�6ијёе…ҘLUTеҸҜжҸҗй«ҳжҖ§иғҪ并жңҖеӨ§йҷҗеәҰең°йҷҚдҪҺеҠҹиҖ�

е…·жңүйӣҷи§ёзҷ�(fДҒ)еҷЁзҡ„LUTз”ЁдәҺз®ЎйҒ“дёӯеҝғжҮ�(yД«ng)з”�

Block RAMе…·жңүе»Јжіӣзҡ„зІ’еә�

е…·жңүеӯ—зҜҖ(jiГ©)еҜ«дҪҝиғҪзҡ„еҝ«йҖҹBlock RAM

18 KbеЎ������пјҢеҸҜйҒёж“Үз·ЁзЁӢзӮәе…©еҖӢзҚЁз«Ӣзҡ„9 Kb Block RAM

жҷӮйҗҳз®ЎзҗҶе№ійӢӘ(CMT)д»ҘжҸҗй«ҳжҖ§иғҪ

дҪҺеҷӘйҹ�����пјҢйқҲжҙ»зҡ„жҷӮйҗҳ

ж•�(shГ№)еӯ—жҷӮйҗҳз®ЎзҗҶеҷЁ(DCM)ж¶ҲйҷӨдәҶжҷӮйҗҳеҒҸе·®е’ҢеҚ з©әжҜ”еӨұзң�

з”ЁдәҺдҪҺжҠ–еӢ•жҷӮйҗҳзҡ„йҺ–зӣёз’�(huГЎn)(PLL)

е…·жңүеҗҢжҷӮд№ҳжі•пјҢйҷӨжі•е’Ңзӣёз§»зҡ„й »зҺҮеҗҲжҲ�

еҚҒе…ӯеҖӢдҪҺеҒҸ移全еұҖжҷӮйҗҳз¶�(wЗҺng)зө�(luГІ)

з°ЎеҢ–й…ҚзҪ®�����пјҢж”ҜжҢҒдҪҺжҲҗжң¬жЁ�(biДҒo)жә�(zhЗ”n)

2йҮқиҮӘеӢ•жӘўжё¬й…ҚзҪ�

еўһеј·дәҶиЁӯ(shГЁ)иЁҲдҝқиӯ·зҡ„е®үе…ЁжҖ�

жҘ�(yГЁ)з•Ңй ҳ(lЗҗng)е…Ҳзҡ„IPе’ҢеҸғиҖғиЁӯ(shГЁ)иЁ�

еӨ§еһӢиЁ�(shГЁ)еӮҷдёӯзҡ„AESжҜ”зү№жөҒеҠ еҜ�

еҠҹиғҪиұҗеҜҢзҡ„Xilinx Platform Flashе’ҢJTAG

з”ЁдәҺиЁ�(shГЁ)иЁҲй©—иӯүзҡ„е”ҜдёҖиЁ�(shГЁ)еӮҷDNAжЁ�(biДҒo)иӯҳз¬Ұ

е»Јжіӣзҡ„第дёүж–№SPI(жңҖй«ҳx4)е’ҢNORй–ғеӯҳж”ҜжҢҒ

жҺӣиө·жЁЎејҸйҖҡйҒҺеӨҡеј•и…іе–ҡйҶ������пјҢжҺ§еҲ¶еўһеј·дҫҶз¶ӯжҢҒзӢҖж…�(tГ i)е’Ңй…ҚзҪ�

MultiBootж”ҜжҢҒдҪҝз”ЁзңӢй–ҖзӢ—дҝқиӯ·йҖІиЎҢеӨҡжҜ”зү№жөҒзҡ„йҒ зЁӢеҚҮзҙ�

йҖҡйҒҺеўһеј·зҡ„дҪҺжҲҗжң¬MicroBlaze?и»ҹиҷ•зҗҶеҷЁеҜҰзҸҫ(xiГ n)жӣҙеҝ«зҡ„еөҢе…ҘејҸиҷ•зҗҶ

й«ҳйҖҹжҺҘеҸЈеҢ…жӢ¬пјҡдёІиЎҢATA���пјҢAurora�пј�1Gд»ҘеӨӘз¶�(wЗҺng)пјҢPCI

Express��пјҢOBSAI��пјҢCPRI�����пјҢEPON�����пјҢGPON����пјҢDisplayPortе’ҢXAUI

жҷӮй–“пј�2023/8/7 16:44:44

жҷӮй–“пј�2023/8/7 16:44:44

й–ұи®Җпј�449

й–ұи®Җпј�449