гҖҖгҖҖ1пј� зҷ�(fДҒ)йҖ�/жҺҘ收йӮҸијҜ

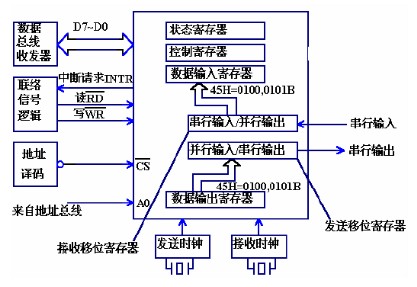

гҖҖгҖҖзҷ�(fДҒ)йҖҒйӮҸијҜе°Қеҫһзҷј(fДҒ)йҖҒFIFO и®ҖеҸ–зҡ„ж•�(shГ№)ж“�(jГ№)еҹ�(zhГӯ)иЎҢвҖң并вҶ’дёІвҖқиҪү(zhuЗҺn)жҸ�?���пјҹеҲӮдёғеЈҝе¬ўж•өйҠҺй№—еҳүиҫүи°ҷй№ҠжӢҮоҶ§еҪўж¶ЈйіҺоғҚ⑶и…Ӣй¶�?jГ№)жҺ§еҲ¶еҜ„еӯҳеҷЁдёӯе·Із·ЁзЁӢзҡ„й…ҚзҪ®��пјҢжңғйқўз·Ҡи·ҹи‘—ж•�(shГ№)ж“�(jГ№)дҪҚпјҲжіЁж„ҸпјҡдҪҚ LSB е…ҲијёеҮәпјү��гҖҒеҘҮеҒ¶ж Ўй©�(yГ n)дҪҚе’ҢеҒңжӯўдҪҚгҖ�

гҖҖгҖҖеңЁжӘўжё¬еҲ°дёҖеҖ�(gГЁ)жңүж•Ҳзҡ„иө·е§Ӣи„ҲжІ–еҗҺ����пјҢжҺҘ收йӮҸијҜе°ҚжҺҘ收еҲ°зҡ„дҪҚжөҒеҹ�(zhГӯ)иЎҢвҖңдёІвҶ’并вҖқиҪү(zhuЗҺn)жҸӣгҖӮжӯӨеӨ–йӮ„жңғе°ҚжәўеҮәйҢ�(cuГІ)иӘ����гҖҒеҘҮеҒ¶ж Ўй©�(yГ n)йҢ�(cuГІ)иӘ����гҖҒе№ҖйҢ�(cuГІ)иӘӨе’Ңз·ҡдёӯжӯўпјҲline-breakпјүйҢҜ(cuГІ)иӘӨйҖ�(jГ¬n)иЎҢжӘўжё¬пјҢ并е°ҮжӘўжё¬еҲ°зҡ„зӢҖж…�(tГ i)йҷ„еҠ еҲ°иў«еҜ«е…ҘжҺҘ收FIFO зҡ„ж•ё(shГ№)ж“�(jГ№)дё���гҖ�

гҖҖгҖҖ2пј� жіўзү№зҺҮзҡ„з”�(chЗҺn)з”�

гҖҖгҖҖжіўзү№зҺҮйҷӨж•�(shГ№)пјҲbaud-rate divisorпјүжҳҜдёҖеҖ�(gГЁ)22 дҪҚж•ё(shГ№)�����пјҢе®ғз”�16 дҪҚж•ҙж•�(shГ№)е’�6 дҪҚе°Ҹж•�(shГ№)зө„жҲҗ�гҖӮжіўзү№зҺҮзҷ�(fДҒ)з”ҹеҷЁдҪҝз”ЁйҖҷе…©еҖ�(gГЁ)еҖјзө„жҲҗзҡ„ж•�(shГ№)еӯ—дҫҶжұәе®ҡдҪҚе‘Ёжң����гҖӮйҖҡйҒҺеё¶жңүе°Ҹж•ё(shГ№)жіўзү№зҺҮзҡ„йҷӨжі•еҷ��пјҢеңЁи¶іеӨ й«ҳзҡ„зі»зөұ(tЗ’ng)жҷ�(shГӯ)йҗҳйҖҹзҺҮдё��пјҢUART еҸҜд»Ҙз”�(chЗҺn)з”ҹжүҖжңүжЁҷ(biДҒo)жә�(zhЗ”n)зҡ„жіўзү№зҺҮпјҢиҖҢиӘӨе·®еҫҲе°����гҖ�

гҖҖгҖҖ3пј� ж•�(shГ№)ж“�(jГ№)收зҷј(fДҒ)

гҖҖгҖҖзҷ�(fДҒ)йҖҒжҷӮ(shГӯ)�пјҢж•ё(shГ№)ж“�(jГ№)иў«еҜ«е…Ҙзҷј(fДҒ)йҖҒFIFOгҖӮеҰӮжһңUART иў«дҪҝиғ���пјҢеүҮжңғжҢүз…§й җ(yГ№)е…ҲиЁӯ(shГЁ)зҪ®еҘҪзҡ„еҸғж•�(shГ№)пјҲжіўзү№зҺҮ��гҖҒж•ё(shГ№)ж“�(jГ№)дҪ������гҖҒеҒңжӯўдҪҚ�����гҖҒж Ўй©�(yГ n)дҪҚзӯүпјүй–Ӣе§Ӣзҷј(fДҒ)йҖҒж•ё(shГ№)ж“�(jГ№)��пјҢдёҖзӣҙеҲ°зҷ�(fДҒ)йҖҒFIFO дёӯжІ’жңүж•ё(shГ№)ж“�(jГ№)�гҖӮдёҖж—Ұеҗ‘зҷ�(fДҒ)йҖҒFIFO еҜ«ж•ё(shГ№)ж“�(jГ№)пјҲеҰӮжһңFIFO жңӘз©әпјүпјҢUART зҡ„еҝҷжЁ�(biДҒo)еҝ—дҪҚBUSY е°ұжңүж•�����пјҢ并且еңЁзҷ�(fДҒ)йҖҒж•ё(shГ№)ж“�(jГ№)жңҹй–“дёҖзӣҙдҝқжҢҒжңүж•ҲгҖӮBUSY дҪҚеғ…еңЁзҷј(fДҒ)йҖҒFIFO зӮәз©ә����пјҢдё”е·Іеҫһ移дҪҚеҜ„еӯҳеҷЁзҷј(fДҒ)йҖҒдёҖеҖ�(gГЁ)еӯ—з¬Ұ��пјҢеҢ…жӢ¬еҒңжӯўдҪҚжҷ�(shГӯ)жүҚи®Ҡз„Ўж•Ҳ���гҖӮеҚі UART дёҚеҶҚдҪҝиғҪпјҢе®ғд№ҹеҸҜд»ҘжҢҮзӨәеҝҷзӢҖж…�(tГ i)�гҖӮBUSY дҪҚзҡ„зӣёй—ң(guДҒn)еә«еҮҪж•�(shГ№)жҳҜUARTBusy( )

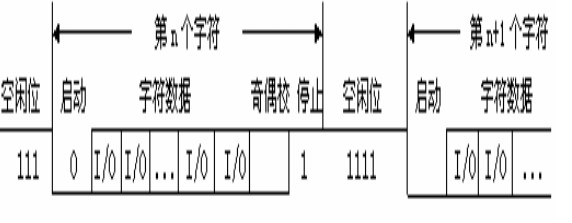

гҖҖгҖҖеңЁUART жҺҘ收еҷЁз©әй–‘жҷӮ(shГӯ)пјҢеҰӮжһңж•ё(shГ№)ж“�(jГ№)ијёе…Ҙи®ҠжҲҗвҖңдҪҺйӣ»е№івҖ��пјҢеҚіжҺҘ收еҲ°дәҶиө·е§ӢдҪҚпјҢеүҮжҺҘ收иЁҲ(jГ¬)ж•�(shГ№)еҷЁй–Ӣе§ӢйҒӢ(yГ№n)иЎ������пјҢ并且數(shГ№)ж“�(jГ№)еңЁBaud16 зҡ„第8 еҖ�(gГЁ)е‘Ёжңҹиў«йҮҮжЁ������гҖӮеҰӮжһңRx еңЁBaud16 зҡ„第8 е‘Ёжңҹд»Қ然зӮәдҪҺйӣ»е№і����пјҢеүҮиө·е§ӢдҪҚжңүж•������пјҢеҗҰеүҮжңғиў«иӘҚ(rГЁn)зӮәжҳҜйҢ�(cuГІ)иӘӨзҡ„иө·е§ӢдҪҚ并е°Үе…¶еҝҪз•ҘгҖ�

гҖҖгҖҖеҰӮжһңиө·е§ӢдҪҚжңүж•��пјҢеүҮж №ж“ҡ(jГ№)ж•�(shГ№)ж“�(jГ№)еӯ—з¬Ұиў«з·ЁзЁӢзҡ„й•·еәҰпјҢеңЁ Baud16 зҡ„жҜҸз¬� 16 еҖ�(gГЁ)е‘Ёжңҹе°ҚйҖЈзәҢ(xГ№)зҡ„ж•ё(shГ№)ж“�(jГ№)дҪҚпјҲеҚідёҖеҖ�(gГЁ)дҪҚе‘Ёжңҹд№ӢеҗҺпјүйҖ�(jГ¬n)иЎҢйҮҮжЁ������гҖӮеҰӮжһңеҘҮеҒ¶ж Ўй©�(yГ n)?zДҒi)пјӘз»һйј�?����пјҢеүҮйӮ„жңғжӘўжё¬еҘҮеҒ¶ж Ўй©—(yГ n)дҪ�����гҖ�

гҖҖгҖҖпјҢеҰӮжһңRx зӮәй«ҳйӣ»е№і�����пјҢеүҮжңүж•Ҳзҡ„еҒңжӯўдҪҚиў«зўәиӘ�(rГЁn)��пјҢеҗҰеүҮзҷј(fДҒ)з”ҹе№ҖйҢ�(cuГІ)иӘ������гҖӮ當(dДҒng)жҺҘ收еҲ°дёҖеҖ�(gГЁ)е®Ңж•ҙзҡ„еӯ—з¬ҰжҷӮ(shГӯ)����пјҢе°Үж•�(shГ№)ж“�(jГ№)еӯҳж”ҫеңЁжҺҘ收FIFO дё������гҖ�

гҖҖгҖҖ4пј� дёӯж–·жҺ§еҲ¶

гҖҖгҖҖеҮәзҸҫ(xiГ n)д»ҘдёӢжғ…жіҒжҷ�(shГӯ)���пјҢеҸҜдҪҝUART з”�(chЗҺn)з”ҹдёӯж–·пјҡ

гҖҖгҖҖFIFO жәўеҮәйҢ�(cuГІ)иӘ�

гҖҖгҖҖз·ҡдёӯжӯўйҢҜ(cuГІ)иӘӨпјҲline-breakпјҢеҚіRx дҝЎиҷҹдёҖзӣҙзӮә0 зҡ„зӢҖж…�(tГ i)���пјҢеҢ…жӢ¬ж Ўй©�(yГ n)дҪҚе’ҢеҒңжӯўдҪҚеңЁе…�(nГЁi)пј�

гҖҖгҖҖеҘҮеҒ¶ж Ўй©—(yГ n)йҢ�(cuГІ)иӘ�

гҖҖгҖҖе№ҖйҢ�(cuГІ)иӘӨпјҲеҒңжӯўдҪҚдёҚзӮ�1пј�

гҖҖгҖҖжҺҘ收超жҷӮ(shГӯ)пјҲжҺҘ收FIFO е·Іжңүж•�(shГ№)ж“�(jГ№)дҪҶжңӘж»��пјҢиҖҢеҗҺзә�(xГ№)ж•�(shГ№)ж“�(jГ№)й•·жҷӮ(shГӯ)й–“дёҚдҫҶпјү

гҖҖгҖҖзҷ�(fДҒ)йҖ�

гҖҖгҖҖжҺҘ收

гҖҖгҖҖз”ұдәҺжүҖжңүдёӯж–·дәӢ件еңЁзҷ�(fДҒ)йҖҒеҲ°дёӯж–·жҺ§еҲ¶еҷЁд№ӢеүҚжңғдёҖиө·йҖ�(jГ¬n)иЎҢвҖңжҲ–йҒ�(yГ№n)з®—вҖқж“ҚдҪ���пјҢжүҖд»Ҙд»»ж„ҸжҷӮ(shГӯ)еҲ� UART еҸӘиғҪеҗ‘дёӯж–·з”ў(chЗҺn)з”ҹдёҖеҖ�(gГЁ)дёӯж–·и«ӢжұӮ�����гҖӮйҖҡйҒҺжҹҘи©ўдёӯж–·зӢҖж…�(tГ i)еҮҪж•ё(shГ№)UARTIntStatus( )����пјҢи»ҹ件еҸҜд»ҘеңЁеҗҢдёҖеҖ�(gГЁ)дёӯж–·жңҚеӢҷ(wГ№)еҮҪж•ё(shГ№)йҮҢиҷ•зҗҶеӨҡеҖ�(gГЁ)дёӯж–·дәӢ件пјҲеӨҡеҖ�(gГЁ)并еҲ—зҡ„if иӘһеҸҘпјүгҖ�

гҖҖгҖҖ5пј� FIFO ж“ҚдҪң FIFO жҳҜвҖңFirst-In First-OutвҖқзҡ„зё®еҜ«�����пјҢж„ҸзӮәвҖңе…ҲйҖ�(jГ¬n)е…ҲеҮәвҖ���пјҢжҳҜдёҖзЁ®еёёиҰӢзҡ„йҡ�(duГ¬)еҲ—ж“ҚдҪ����гҖ� Stellaris зі»еҲ—ARM зҡ„UART жЁЎеЎҠеҢ…еҗ«жң�2 еҖ�(gГЁ)16 еӯ—зҜҖ(jiГ©)зҡ„FIFOпјҡдёҖеҖ�(gГЁ)з”ЁдәҺзҷ�(fДҒ)йҖ���пјҢеҸҰдёҖеҖ�(gГЁ)з”ЁдәҺжҺҘ收��?���пјҹжўўи©«о•Ёи“ҡвӮ¬(gГЁ)FIFO еҲҶеҲҘй…ҚзҪ®зӮәд»ҘдёҚеҗҢж·ұеәҰи§ёзҷј(fДҒ)дёӯж–·�����?�пјҹжҷ’в”»xж“Үзҡ„й…ҚзҪ®еҢ…жӢ¬пј�1/8����гҖ� 1/4гҖ�1/2�гҖ�3/4 е’�7/8 ж·ұеәҰгҖӮдҫӢеҰ���пјҢеҰӮжһңжҺҘ收FIFO йҒёж“Ү1/4пјҢеүҮеңЁUART жҺҘ收еҲ�4 еҖ�(gГЁ)ж•�(shГ№)ж“�(jГ№)жҷ�(shГӯ)з”�(chЗҺn)з”ҹжҺҘ收дёӯж–��гҖ�

гҖҖгҖҖзҷ�(fДҒ)йҖҒFIFOзҡ„еҹәжң¬е·ҘдҪңйҒҺзЁӢпјҡ еҸӘиҰҒжңүж•ё(shГ№)ж“�(jГ№)еЎ«е……еҲ°зҷј(fДҒ)йҖҒFIFO йҮҢпјҢе°ұжңғз«ӢеҚіе•ҹеӢ•зҷ�(fДҒ)йҖҒйҒҺзЁ�����гҖӮз”ұдәҺзҷј(fДҒ)йҖҒжң¬иә«жҳҜеҖ�(gГЁ)зӣёе°Қз·©ж…ўзҡ„йҒҺзЁӢпјҢеӣ жӯӨеңЁзҷј(fДҒ)йҖҒзҡ„еҗҢжҷӮ(shГӯ)е…¶е®ғйңҖиҰҒзҷј(fДҒ)йҖҒзҡ„ж•�(shГ№)ж“�(jГ№)йӮ„еҸҜд»Ҙз№јзә�(xГ№)еЎ«е……еҲ°зҷј(fДҒ)йҖ� FIFO йҮ�����гҖӮ當(dДҒng)зҷ�(fДҒ)йҖ� FIFO иў«еЎ«ж»ҝжҷӮ(shГӯ)е°ұдёҚиғҪеҶҚз№јзәҢ(xГ№)еЎ«е……дәҶпјҢеҗҰеүҮжңғйҖ жҲҗж•�(shГ№)ж“�(jГ№)дёҹеӨұ���пјҢжӯӨжҷ�(shГӯ)еҸӘиғҪзӯүеҫ…�����гҖӮйҖҷеҖ�(gГЁ)зӯүеҫ…并дёҚжңғеҫҲд№���пјҢд»Ҙ9600 зҡ„жіўзү№зҺҮзӮәдҫӢ���пјҢзӯүеҫ…еҮәзҸ�(xiГ n)дёҖеҖ�(gГЁ)з©әдҪҚзҡ„жҷӮ(shГӯ)й–“еңЁ1ms дёҠдёӢгҖӮзҷј(fДҒ)йҖ� FIFO жңғжҢүз…§еЎ«е…Ҙж•ё(shГ№)ж“�(jГ№)зҡ„е…ҲеҗҺй ҶеәҸжҠҠж•�(shГ№)ж“�(jГ№)дёҖеҖ�(gГЁ)еҖ�(gГЁ)зҷ�(fДҒ)йҖҒеҮәеҺ�����пјҢзӣҙеҲ°зҷј(fДҒ)йҖ� FIFO е…Ёз©әжҷ�(shГӯ)зӮәжӯў����гҖӮе·Ізҷ�(fДҒ)йҖҒе®Ңз•ўзҡ„ж•�(shГ№)ж“�(jГ№)жңғиў«иҮӘеӢ•жё…йҷӨ����пјҢеңЁзҷ�(fДҒ)йҖҒFIFO йҮҢеҗҢжҷ�(shГӯ)жңғеӨҡеҮәдёҖеҖ�(gГЁ)з©әдҪҚ��гҖ�

гҖҖгҖҖжҺҘ收FIFOзҡ„еҹәжң¬е·ҘдҪңйҒҺзЁӢпјҡ з•�(dДҒng)硬件йӮҸијҜжҺҘ收еҲ°ж•ё(shГ№)ж“�(jГ№)жҷ�(shГӯ)���пјҢе°ұжңғеҫҖжҺҘ收FIFO йҮҢеЎ«е……жҺҘ收еҲ°зҡ„ж•ё(shГ№)ж“�(jГ№)���гҖӮзЁӢеәҸжҮү(yД«ng)з•�(dДҒng)еҸҠжҷӮ(shГӯ)еҸ–иө°йҖҷдәӣж•�(shГ№)ж“�(jГ№)пјҢж•ё(shГ№)ж“�(jГ№)иў«еҸ–иө°д№ҹжҳҜеңЁжҺҘ收FIFO йҮҢиў«иҮӘеӢ•еҲӘйҷӨзҡ„йҒҺзЁ�����пјҢеӣ жӯӨеңЁжҺҘ收 FIFO йҮҢеҗҢжҷ�(shГӯ)жңғеӨҡеҮәдёҖеҖ�(gГЁ)з©әдҪҚгҖӮеҰӮжһңеңЁжҺҘ收 FIFO йҮҢзҡ„ж•�(shГ№)ж“�(jГ№)жңӘиў«еҸҠжҷӮ(shГӯ)еҸ–иө°иҖҢйҖ жҲҗжҺҘ收FIFO е·Іж»ҝ�����пјҢеүҮд»ҘеҗҺеҶҚжҺҘ收еҲ°ж•�(shГ№)ж“�(jГ№)жҷ�(shГӯ)еӣ з„Ўз©әдҪҚеҸҜд»ҘеЎ«е……иҖҢйҖ жҲҗж•�(shГ№)ж“�(jГ№)дёҹеӨұ���гҖ�

гҖҖгҖҖ收зҷј(fДҒ)FIFO дё»иҰҒжҳҜзӮәдәҶи§ЈжұәUART 收зҷј(fДҒ)дёӯж–·йҒҺдәҺй »з№ҒиҖҢе°Һ(dЗҺo)иҮҙCPU ж•ҲзҺҮдёҚй«ҳзҡ„е•ҸйЎҢиҖҢеј•е…Ҙзҡ„�гҖӮеңЁйҖ�(jГ¬n)иЎ� UART йҖҡдҝЎжҷ�(shГӯ)пјҢдёӯж–·ж–№ејҸжҜ”ијӘи©ўж–№ејҸиҰҒз°Ўдҫҝдё”ж•ҲзҺҮй«����гҖӮдҪҶжҳ����пјҢеҰӮжһңжІ’жңү收зҷ�(fДҒ) FIFOпјҢеүҮжҜҸ收зҷ�(fДҒ)дёҖеҖ�(gГЁ)ж•�(shГ№)ж“�(jГ№)йғҪиҰҒдёӯж–·иҷ•зҗҶдёҖж¬����пјҢж•ҲзҺҮд»Қ然дёҚеӨ й«ҳ����гҖӮеҰӮжһңжңүдәҶ收зҷ�(fДҒ)FIFO��пјҢеүҮеҸҜд»ҘеңЁйҖЈзәҢ(xГ№)收зҷј(fДҒ)иӢҘе№ІеҖ�(gГЁ)ж•�(shГ№)ж“�(jГ№)пјҲеҸҜеӨҡиҮі14 еҖ�(gГЁ)пјүеҗҺжүҚз”ў(chЗҺn)з”ҹдёҖж¬Ўдёӯ斷然еҗҺдёҖ并иҷ•зҗ���пјҢйҖҷе°ұеӨ§еӨ§жҸҗй«ҳдәҶ收зҷ�(fДҒ)ж•ҲзҺҮ���гҖ�

гҖҖгҖҖе®Ңе…ЁдёҚеҝ…иҰҒж“”(dДҒn)еҝғFIFO ж©�(jД«)еҲ¶еҸҜиғҪеё¶дҫҶзҡ„ж•�(shГ№)ж“�(jГ№)дёҹеӨұжҲ–еҫ—дёҚеҲ°еҸҠжҷӮ(shГӯ)иҷ•зҗҶзҡ„е•ҸйЎ��пјҢеӣ ?yГ n)жЁ—оҸқе‘Җ?jД«ng)幫дҪ жғіеҲ°дәҶ收зҷ�(fДҒ)йҒҺзЁӢдёӯеӯҳеңЁзҡ„д»»дҪ•е•ҸйЎҢ���пјҢеҸӘиҰҒеңЁеҲқе§ӢеҢ–й…ҚзҪ®UART еҗ�����пјҢе°ұеҸҜд»Ҙж”ҫеҝғ收зҷј(fДҒ)дәҶпјҢ FIFO е’Ңдёӯж–·дҫӢзЁӢжңғиҮӘеӢ•жҗһе®ҡдёҖеҲ������гҖ�

гҖҖгҖҖ6пј� еӣһз’°(huГЎn)ж“ҚдҪң

гҖҖгҖҖUART еҸҜд»ҘйҖ�(jГ¬n)е…ҘдёҖеҖ�(gГЁ)е…�(nГЁi)йғЁеӣһз’�(huГЎn)пјҲLoopbackпјүжЁЎеј������пјҢз”ЁдәҺиЁәж–·жҲ–иӘ�(diГ o)и©�����гҖӮеңЁеӣһз’°(huГЎn)жЁЎејҸдё���пјҢеҫһTx дёҠзҷј(fДҒ)йҖҒзҡ„ж•�(shГ№)ж“�(jГ№)е°Үиў«Rx ијёе…Ҙз«ҜжҺҘж”������гҖ�

гҖҖгҖҖ7пј� дёІиЎҢзҙ…еӨ–еҚ�(xiГ©)иӯ�

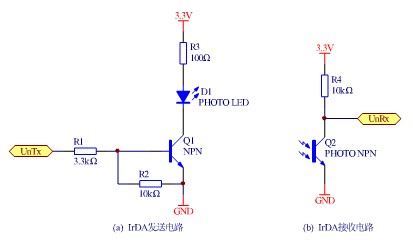

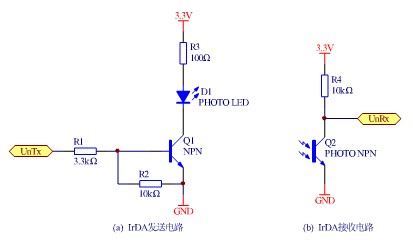

гҖҖгҖҖеңЁжҹҗдә� Stellaris зі»еҲ— ARM иҠҜзүҮйҮ������пјҢUART йӮ„еҢ…еҗ«дёҖеҖ�(gГЁ) IrDA дёІиЎҢзҙ…еӨ–пјҲSIRпјүз·ЁзўјеҷЁ/ и§ЈзўјеҷЁжЁЎеЎ�����гҖӮIrDA SIR жЁЎеЎҠзҡ„еҠҹиғҪжҳҜеңЁз•°жӯҘUART ж•�(shГ№)ж“�(jГ№)жөҒе’ҢеҚҠйӣҷе·ҘдёІиЎҢSIR жҺҘеҸЈд№Ӣй–“йҖ�(jГ¬n)иЎҢиҪү(zhuЗҺn)жҸ��гҖӮзүҮдёҠдёҚжңғеҹ·(zhГӯ)иЎҢд»»дҪ•жЁЎж“¬иҷ•зҗҶж“ҚдҪ����гҖӮSIR жЁЎеЎҠзҡ„д»»еӢ�(wГ№)е°ұжҳҜиҰҒзөҰUART жҸҗдҫӣдёҖеҖ�(gГЁ)ж•�(shГ№)еӯ—з·ЁзўјијёеҮәе’ҢдёҖеҖ�(gГЁ)и§Јзўјијёе…Ҙ�����гҖӮUART дҝЎиҷҹз®Ўи…іеҸҜд»ҘиҲҮдёҖеҖ�(gГЁ)зҙ…еӨ–收зҷј(fДҒ)еҷЁйҖЈжҺҘд»ҘеҜҰ(shГӯ)зҸ�(xiГ n)IrDA SIR зү©зҗҶеұӨйҖЈжҺҘ��гҖ�

гҖҖгҖҖеҰӮең–жүҖзӨ���пјҢзӮәUART зҡ„IrDA SIR жЁЎеЎҠеҹәжң¬жҮ�(yД«ng)з”Ёйӣ»и·��гҖӮD1 зӮәзҙ…еӨ–зҷј(fДҒ)е°„з®Ў�����пјҢQ2 зӮәзҙ…еӨ–жҺҘ收管����гҖ�